6.1 Introducció

Els ordinadors moderns de propòsit general són de dos tipus: CISC i RISC. CISC són les sigles de Complex Instruction Set Computer. RISK són les sigles de Reduced Instruction Set Computer. Els microprocessadors 6502 o 6510, segons sigui aplicable a l'ordinador Commodore-64, s'assemblen més a l'arquitectura RISC que a una arquitectura CISC.

Els ordinadors RISC generalment tenen instruccions de llenguatge ensamblador més curts (per nombre de bytes) en comparació amb els ordinadors CISC.

Nota : Tant si es tracta de CISC, RISC o ordinador antic, un perifèric comença des d'un port intern i surt a través d'un port extern a la superfície vertical de la unitat del sistema de l'ordinador (unitat base) i al dispositiu extern.

Una instrucció típica d'un ordinador CISC es pot veure com unir diverses instruccions breus de llenguatge ensamblador en una instrucció de llenguatge ensamblador més llarga que fa que la instrucció resultant sigui complexa. En particular, un ordinador CISC carrega els operands de la memòria als registres del microprocessador, realitza una operació i després emmagatzema el resultat a la memòria, tot en una instrucció. D'altra banda, es tracta d'almenys tres instruccions (abreviades) per a l'ordinador RISC.

Hi ha dues sèries populars d'ordinadors CISC: els ordinadors amb microprocessador Intel i els ordinadors amb microprocessador AMD. AMD significa Advanced Micro Devices; és una empresa de fabricació de semiconductors. Les sèries de microprocessadors intel, per ordre de desenvolupament, són 8086, 8088, 80186, 80286, 80386, 80486, Pentium, Core, i Series, Celeron i Xeon. Les instruccions del llenguatge assemblador per als primers microprocessadors intel, com ara 8086 i 8088, no són gaire complexes. No obstant això, són complexos per als nous microprocessadors. Els recents microprocessadors AMD per a la sèrie CISC són Ryzen, Opteron, Athlon, Turion, Phenom i Sempron. Els microprocessadors Intel i AMD es coneixen com a microprocessadors x86.

ARM significa Advanced RISC Machine. Les arquitectures ARM defineixen una família de processadors RISC adequats per al seu ús en una gran varietat d'aplicacions. Mentre que molts microprocessadors Intel i AMD s'utilitzen als ordinadors personals d'escriptori, molts processadors ARM serveixen com a processadors incrustats en sistemes crítics per a la seguretat, com ara frens antibloqueig d'automòbils i com a processadors d'ús general en rellotges intel·ligents, telèfons portàtils, tauletes i ordinadors portàtils. . Tot i que els dos tipus de microprocessadors es poden veure en dispositius petits i grans, els microprocessadors RISC es troben més en dispositius petits que en dispositius grans.

Word d'ordinador

Si es diu que un ordinador és un ordinador de paraules de 32 bits, vol dir que la informació s'emmagatzema, es transfereix i es manipula en forma de codis binaris de trenta-dos bits dins de la part interna de la placa base. També significa que els registres de propòsit general del microprocessador de l'ordinador tenen una amplada de 32 bits. Els registres A, X i Y del microprocessador 6502 són registres d'ús general. Tenen vuit bits d'ample, per tant, l'ordinador Commodore-64 és un ordinador de vuit bits.

Una mica de vocabulari

Ordinadors X86

Els significats de byte, word, doubleword, quadword i double-quadword són els següents per als ordinadors x86:

- Byte : 8 bits

- Paraula : 16 bits

- Doble paraula : 32 bits

- Quadword : 64 bits

- Quadre paraula doble : 128 bits

Ordinadors ARM

Els significats de byte, mitja paraula, paraula i paraula doble són els següents per als ordinadors ARM:

- Byte : 8 bits

- Fes-te la meitat : 16 bits

- Paraula : 32 bits

- Doble paraula : 64 bits

Cal tenir en compte les diferències i similituds dels noms (i valors) x86 i ARM.

Nota : Els nombres enters de signe dels dos tipus d'ordinador són complement de dos.

Ubicació de la memòria

Amb l'ordinador Commodore-64, una ubicació de memòria sol ser d'un byte, però podria ser de dos bytes consecutius de tant en tant quan es consideren els punters (adreçament indirecte). Amb un ordinador x86 modern, una ubicació de memòria és de 16 bytes consecutius quan es tracta d'una paraula quàdruple doble de 16 bytes (128 bits), 8 bytes consecutius quan es tracta de paraula quàdruple de 8 bytes (64 bits), 4 bytes consecutius quan es tracta d'una paraula doble de 4 bytes (32 bits), 2 bytes consecutius quan es tracta d'una paraula de 2 bytes (16 bits) i 1 byte quan es tracta d'un byte (8 bits). Amb un ordinador ARM modern, una ubicació de memòria és de 8 bytes consecutius quan es tracta d'una paraula doble de 8 bytes (64 bits), 4 bytes consecutius quan es tracta d'una paraula de 4 bytes (32 bits), 2 bytes consecutius quan es tracta d'una paraula mitjana. de 2 bytes (16 bits) i 1 byte quan es tracta d'un byte (8 bits).

Aquest capítol explica què és comú a les arquitectures CISC i RISC i quines són les seves diferències. Això es fa en comparació amb el 6502 µP i l'ordinador commodore-64 on sigui aplicable.

6.2 Diagrama de blocs de la placa base de l'ordinador modern

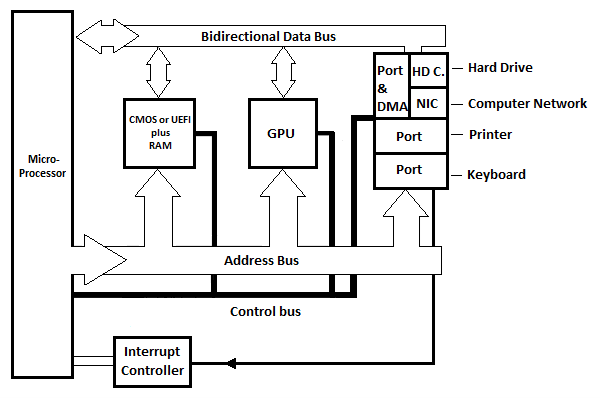

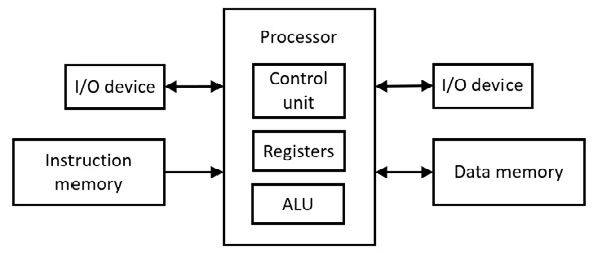

PC significa ordinador personal. El següent és un diagrama de blocs bàsic genèric per a una placa base moderna amb un únic microprocessador per a un ordinador personal. Representa una placa base CISC o RISC.

Fig. 6.21 Diagrama de blocs bàsic de la placa base de l'ordinador modern

Al diagrama es mostren tres ports interns, però a la pràctica n'hi ha més. Cada port té un registre que es pot veure com el propi port. Cada circuit de port té almenys un altre registre que es pot anomenar 'registre d'estat'. El registre d'estat indica el port al programa que envia el senyal d'interrupció al microprocessador. Hi ha un circuit de controlador d'interrupció (no mostrat) que diferencia entre les diferents línies d'interrupció dels diferents ports i només té unes poques línies al µP.

HD.C al diagrama significa Targeta de disc dur. NIC són les sigles de Network Interface Card. La targeta del disc dur (circuit) està connectada al disc dur que es troba dins de la unitat base (unitat del sistema) de l'ordinador modern. La targeta d'interfície de xarxa (circuit) es connecta mitjançant un cable extern a un altre ordinador. Al diagrama, hi ha un port i un DMA (consulteu la il·lustració següent) connectats a la targeta de disc dur i/o a la targeta d'interfície de xarxa. El DMA significa Accés directe a la memòria.

Recordeu del capítol d'ordinador Commodore-64 que per enviar els bytes de la memòria a la unitat de disc o a un altre ordinador, cada byte s'ha de copiar a un registre del microprocessador abans de ser copiat al port intern corresponent, i després automàticament. al dispositiu. Per rebre els bytes de la unitat de disc o un altre ordinador a la memòria, cada byte s'ha de copiar des del registre del port intern corresponent a un registre del microprocessador abans de copiar-se a la memòria. Això normalment triga molt si el nombre de bytes del flux és gran. La solució per a la transferència ràpida és l'ús de l'accés directe a la memòria (circuit) sense passar pel microprocessador.

El circuit DMA es troba entre el port i l'HD. C o NIC. Amb l'accés directe a la memòria del circuit DMA, la transferència de grans fluxos de bytes es fa directament entre el circuit DMA i la memòria (RAM) sense la participació continuada del microprocessador. El DMA utilitza el bus d'adreces i el bus de dades en lloc de µP. La durada total de la transferència és més curta que si s'hagués d'utilitzar el µP dur. Tant la HD C. com la NIC utilitzen el DMA quan tenen un gran flux de dades (bytes) per a la transferència amb RAM (la memòria).

GPU són les sigles de Graphics Processing Unit. Aquest bloc de la placa base s'encarrega d'enviar el text i les imatges en moviment o fixes a la pantalla.

Amb els ordinadors moderns (PC), no hi ha memòria de només lectura (ROM). Hi ha, però, la BIOS o UEFI que és una mena de RAM no volàtil. La informació de la BIOS es manté en realitat per una bateria. La bateria és el que en realitat manté el temporitzador del rellotge també, a l'hora i la data adequades per a l'ordinador. UEFI es va inventar després de la BIOS i ha substituït la BIOS, tot i que la BIOS encara és força rellevant als ordinadors moderns. En parlarem més endavant!

En els ordinadors moderns, els busos d'adreces i dades entre el µP i els circuits del port intern (i la memòria) no són busos paral·lels. Són busos sèrie que necessiten dos conductors per a la transmissió en un sentit i altres dos conductors per a la transmissió en sentit contrari. Això significa, per exemple, que es poden enviar 32 bits en sèrie (un bit després de l'altre) en qualsevol direcció.

Si la transmissió en sèrie només és en una direcció amb dos conductors (dues línies), es diu que és semidúplex. Si la transmissió en sèrie és en ambdues direccions amb quatre conductors, un parell en qualsevol direcció, es diu que és full-duplex.

Tota la memòria de l'ordinador modern encara consta d'una sèrie d'ubicacions de bytes: vuit bits per byte. Un ordinador modern té un espai de memòria d'almenys 4 giga bytes = 4 x 210 x 2 10 x 2 10 = 4 x 1.073.741.824 10 bytes = 4 x 1024 10/sub> x 1024 10 x 1024 10 = 4 x 1.073.741.824 10 .

Nota : Tot i que no es mostra cap circuit de temporitzador a la placa base anterior, totes les plaques base modernes tenen circuits de temporitzador.

6.3 Conceptes bàsics d'arquitectura d'ordinadors x64

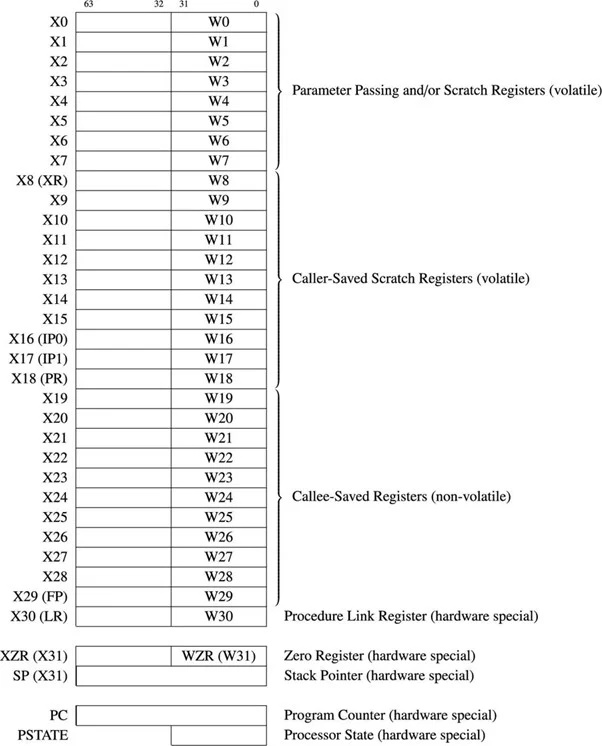

6.31 El conjunt de registres x64

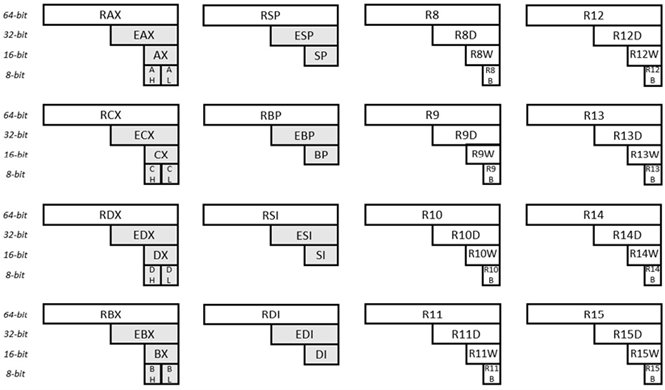

El microprocessador de 64 bits de la sèrie de microprocessadors x86 és un microprocessador de 64 bits. És força modern per substituir el processador de 32 bits de la mateixa sèrie. Els registres de propòsit general del microprocessador de 64 bits i els seus noms són els següents:

Fig. 6.31 Registres d'ús general per a x64

A la il·lustració es mostren setze (16) registres de propòsit general. Cadascun d'aquests registres té una amplada de 64 bits. Mirant el registre a la cantonada superior esquerra, els 64 bits s'identifiquen com a RAX. Els primers 32 bits d'aquest mateix registre (des de la dreta) s'identifiquen com a EAX. Els primers 16 bits d'aquest mateix registre (des de la dreta) s'identifiquen com a AX. El segon byte (des de la dreta) d'aquest mateix registre s'identifica com AH (H aquí significa alt). I el primer byte (d'aquest mateix registre) s'identifica com AL (L aquí significa baix). Mirant el registre a la cantonada inferior dreta, els 64 bits s'identifiquen com a R15. Els primers 32 bits d'aquest mateix registre s'identifiquen com a R15D. Els primers 16 bits d'aquest mateix registre s'identifiquen com a R15W. I el primer byte s'identifica com a R15B. Els noms dels altres registres (i subregistres) s'expliquen de la mateixa manera.

Hi ha algunes diferències entre els µP d'Intel i d'AMD. La informació d'aquesta secció és per a Intel.

Amb el 6502 µP, el registre del comptador de programes (no accessible directament) que conté la següent instrucció a executar té 16 bits d'ample. Aquí (x64), el comptador del programa s'anomena punter d'instruccions i té una amplada de 64 bits. Està etiquetat com a RIP. Això vol dir que el x64 µP pot adreçar fins a 264 = 1,844674407 x 1019 (en realitat 18.446.744.073.709.551.616) ubicacions de bytes de memòria. RIP no és un registre d'ús general.

El registre Stack Pointer o RSP es troba entre els 16 registres de propòsit general. Apunta a l'última entrada de pila de la memòria. Igual que amb 6502 µP, la pila per a x64 creix cap avall. Amb el x64, la pila de la memòria RAM s'utilitza per emmagatzemar les adreces de retorn de les subrutines. També s'utilitza per emmagatzemar l''espai d'ombra' (consulteu la discussió següent).

El 6502 µP té un registre d'estat del processador de 8 bits. L'equivalent al x64 s'anomena registre RFLAGS. Aquest registre emmagatzema els indicadors que s'utilitzen per als resultats de les operacions i per controlar el processador (µP). Té una amplada de 64 bits. Els 32 bits més alts estan reservats i no s'utilitzen actualment. La taula següent ofereix els noms, l'índex i els significats dels bits utilitzats habitualment al registre RFLAGS:

| Taula 6.31.1 Senyals RFLAGS més utilitzats (bits) |

|||

|---|---|---|---|

| Símbol | Bit | Nom | Propòsit |

| CF | 0 | Portar | S'estableix si una operació aritmètica genera un acarreament o un préstec del bit més significatiu del resultat; esborrat en cas contrari. Aquest senyalador indica una condició de desbordament per a l'aritmètica de nombres enters sense signe. També s'utilitza en aritmètica de precisió múltiple. |

| PF | 2 | Paritat | S'estableix si el byte menys significatiu del resultat conté un nombre parell d'1 bits; esborrat en cas contrari. |

| DE | 4 | Ajustar | S'estableix si una operació aritmètica genera un acarreament o un préstec del bit 3 del resultat; esborrat en cas contrari. Aquesta bandera s'utilitza en l'aritmètica decimal codificat binari (BCD). |

| ZF | 6 | Zero | S'estableix si el resultat és zero; esborrat en cas contrari. |

| SF | 7 | Signe | S'estableix si és igual al bit més significatiu del resultat que és el bit de signe d'un nombre enter amb signe (0 indica un valor positiu i 1 un valor negatiu). |

| DE | 11 | Desbordament | S'estableix si el resultat sencer és un nombre positiu massa gran o un nombre negatiu massa petit (excloent el bit de signe) per cabre a l'operand de destinació; esborrat en cas contrari. Aquest indicador indica una condició de desbordament per a l'aritmètica d'enteris amb signe (complement de dos). |

| DF | 10 | Direcció | S'estableix si les instruccions de la cadena de direcció funcionen (increment o disminució). |

| ID | 21 | Identificació | S'estableix si la seva variabilitat denota la presència de la instrucció CPUID. |

A més dels divuit registres de 64 bits que s'han indicat anteriorment, l'arquitectura x64 µP té vuit registres de 80 bits d'ample per a l'aritmètica de coma flotant. Aquests vuit registres també es poden utilitzar com a registres MMX (consulteu la discussió següent). També hi ha setze registres de 128 bits per a XMM (consulteu la discussió següent).

Això no és tot sobre registres. Hi ha més registres x64 que són registres de segments (majoritàriament no utilitzats a x64), registres de control, registres de gestió de memòria, registres de depuració, registres de virtualització, registres de rendiment que fan un seguiment de tot tipus de paràmetres interns (errors de memòria cau, microoperacions executades, sincronització). , i molt més).

SIMD

SIMD són les sigles de Single Instruction Multiple Data. Això vol dir que una instrucció de llenguatge ensamblador pot actuar sobre diverses dades al mateix temps en un microprocessador. Considereu la taula següent:

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | |

| + | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

| = | 10 | 12 | 14 | 16 | 18 | 20 | 22 | 24 |

En aquesta taula, s'afegeixen vuit parells de nombres en paral·lel (en la mateixa durada) per donar vuit respostes. Una instrucció de llenguatge ensamblador pot fer les vuit addicions d'enters paral·lels als registres MMX. Una cosa semblant es pot fer amb els registres XMM. Per tant, hi ha instruccions MMX per a nombres enters i instruccions XMM per a flotants.

6.32 Mapa de memòria i x64

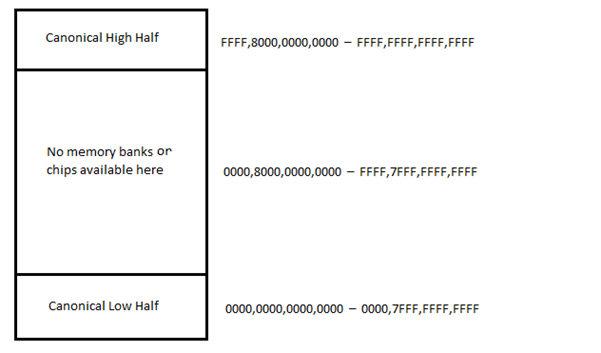

Amb el punter d'instruccions (comptador de programa) que té 64 bits, això significa que es poden adreçar ubicacions de bytes de memòria 264 = 1,844674407 x 1019. En hexadecimal, la ubicació de bytes més alta és FFFF,FFFF,FFFF,FFFF16. Cap ordinador normal d'avui pot proporcionar un espai de memòria (complet) tan gran. Per tant, un mapa de memòria adequat per a l'ordinador x64 és el següent:

Tingueu en compte que el buit de 0000,8000,0000,000016 a FFFF,7FFF,FFFF,FFFF16 no té ubicacions de memòria (sense bancs de memòria RAM). Aquesta és una diferència de FFFF,0000,0000,000116 que és força gran. La meitat alta canònica té el sistema operatiu, mentre que la meitat baixa canònica té els programes d'usuari (aplicacions) i les dades. El sistema operatiu consta de dues parts: una petita UEFI (BIOS) i una gran part que es carreguen des del disc dur. El següent capítol parla més sobre els sistemes operatius moderns. Tingueu en compte la similitud amb aquest mapa de memòria i la del Commodore-64 quan 64KB podria haver semblat molta memòria.

En aquest context, el sistema operatiu s'anomena aproximadament 'nucli'. El nucli és similar al nucli de l'ordinador Commodore-64, però té moltes més subrutines.

L'endianness per a x64 és little endian, el que significa que per a una ubicació, l'adreça inferior apunta al byte de contingut més baix de la memòria.

6.33 Modes d'adreçament en llenguatge ensamblador per a x64

Els modes d'adreçament són les maneres en què una instrucció pot accedir als registres µP i a la memòria (inclosos els registres del port intern). El x64 té molts modes d'adreçament, però aquí només s'aborden els modes d'adreçament utilitzats habitualment. La sintaxi general d'una instrucció aquí és:

opcode destinació, font

Els nombres decimals s'escriuen sense cap prefix ni sufix. Amb el 6502, la font és implícita. El x64 té més codis operatius que el 6502, però alguns dels codis operatius tenen els mateixos mnemotècnics. Les instruccions x64 individuals són de longitud variable i poden variar de 1 a 15 bytes. Els modes d'adreçament utilitzats habitualment són els següents:

Mode d'adreçament immediat

Aquí, l'operand font és un valor real i no una adreça o etiqueta. Exemple (llegiu el comentari):

AFEGIR EAX, 14; afegiu un decimal de 14 a 32 bits EAX de 64 bits RAX, la resposta roman a EAX (destinació)

Registreu-vos per registrar el mode d'adreçament

Exemple:

ADD R8B, AL ; afegiu AL de 8 bits de RAX a R8B de R8 de 64 bits: les respostes romanen a R8B (destinació)

Mode d'adreçament indirecte i indexat

L'adreçament indirecte amb el 6502 µP significa que la ubicació de l'adreça donada a la instrucció té l'adreça efectiva (punter) de la ubicació final. Una cosa semblant passa amb x64. L'adreçament d'índex amb el 6502 µP significa que el contingut d'un registre µP s'afegeix a l'adreça donada a la instrucció per tenir l'adreça efectiva. Una cosa semblant passa amb el x64. A més, amb el x64, el contingut del registre també es pot multiplicar per 1 o 2 o 4 o 8 abans de ser afegit a l'adreça indicada. La instrucció mov (còpia) del x64 pot combinar adreçament indirecte i indexat. Exemple:

MOV R8W, 1234[8*RAX+RCX] ; mou la paraula a l'adreça (8 x RAX + RCX) + 1234

Aquí, R8W té els primers 16 bits de R8. L'adreça donada és 1234. El registre RAX té un número de 64 bits que es multiplica per 8. El resultat s'afegeix al contingut del registre RCX de 64 bits. Aquest segon resultat s'afegeix a l'adreça proporcionada que és 1234 per obtenir l'adreça efectiva. El número a la ubicació de l'adreça efectiva es mou (copia) al primer lloc de 16 bits (R8W) del registre R8, substituint el que hi havia. Observeu l'ús dels claudàtors. Recordeu que una paraula en x64 té 16 bits d'amplada.

RIP Adreçament relatiu

Per al 6502 µP, l'adreçament relatiu només s'utilitza amb instruccions de branca. Allà, l'únic operand del codi operatiu és un desplaçament que s'afegeix o es resta al contingut del comptador de programa per a l'adreça d'instrucció efectiva (no l'adreça de dades). Una cosa semblant passa amb el x64 on el comptador de programa s'anomena punter d'instruccions. La instrucció amb x64 no només ha de ser una instrucció de branca. Un exemple d'adreçament relatiu a RIP és:

MOV AL, [RIP]

AL de RAX té un número signat de 8 bits que s'afegeix o es resta del contingut en RIP (punter d'instrucció de 64 bits) per apuntar a la següent instrucció. Tingueu en compte que la font i la destinació s'intercanvien excepcionalment en aquesta instrucció. Tingueu en compte també l'ús dels claudàtors que fan referència al contingut del RIP.

6.34 Instruccions d'ús habitual de x64

A la taula següent, * significa diferents sufixos possibles d'un subconjunt de codis operatius:

| Taula 6.34.1 Instruccions d'ús habitual en x64 |

|

|---|---|

| Opcode | Significat |

| MOV | Moure (copiar) a/des/entre memòria i registres |

| CMOV* | Diversos moviments condicionals |

| XCHG | Intercanvi |

| BSWAP | Intercanvi de bytes |

| PUSH/POP | Ús de la pila |

| ADD/ADC | Afegir/amb portar |

| SUB/SBC | Resta/amb portar |

| MUL/IMUL | Multiplicar/sense signar |

| DIV/IDIV | Dividir/no signar |

| INC/DES | Increment/Disminució |

| NEG | Negar |

| CMP | Compara |

| I/O/XOR/NO | Operacions per bits |

| SHR/SAR | Desplaçament cap a la dreta lògic/aritmètica |

| SHL/SAL | Desplaçament cap a l'esquerra lògic/aritmètica |

| ROR/ROL | Gira a la dreta/esquerra |

| RCR/RCL | Gireu a la dreta/esquerra a través del bit de transport |

| BT/BTS/BTR | Prova de bits/i estableix/i reinicia |

| JMP | Salt incondicional |

| JE/JNE/JC/JNC/J* | Salta si és igual/no és igual/ porta/no porta/molts altres |

| CAMINAR / CAMINAR / CAMINAR | Bucle amb ECX |

| CALL/RET | Subrutina de trucada/retorn |

| NOP | Cap operació |

| CPUID | Informació de la CPU |

El x64 té instruccions de multiplicar i dividir. Té circuits de maquinari de multiplicació i divisió en el seu µP. El 6502 µP no té circuits de maquinari de multiplicació i divisió. És més ràpid fer la multiplicació i la divisió per maquinari que per programari (incloent el desplaçament de bits).

Instruccions de cadena

Hi ha una sèrie d'instruccions de cadena, però l'única que es tractarà aquí és la instrucció MOVS (per a moure cadena) per copiar una cadena que comença a l'adreça C000 H . Per començar a l'adreça C100 H , utilitzeu les instruccions següents:

MOVS [C100H], [C000H]

Tingueu en compte el sufix H per a l'hexadecimal.

6.35 Bucle a x64

El 6502 µP té instruccions de branca per al bucle. Una instrucció de branca salta a una ubicació d'adreça que té la instrucció nova. La ubicació de l'adreça es pot anomenar 'bucle'. El x64 té instruccions LOOP/LOOPE/LOOPNE per fer un bucle. Aquestes paraules reservades en llenguatge ensamblador no s'han de confondre amb l'etiqueta 'bucle' (sense les cometes). El comportament és el següent:

LOOP disminueix ECX i comprova si ECX no és zero. Si es compleix aquesta condició (zero), salta a una etiqueta especificada. En cas contrari, falla (continueu amb la resta d'instruccions a la discussió següent).

LOOPE disminueix l'ECX i comprova que l'ECX no sigui zero (pot ser 1, per exemple) i que ZF estigui establert (a 1). Si es compleixen aquestes condicions, salta a l'etiqueta. En cas contrari, cau.

LOOPNE disminueix ECX i comprova que ECX no sigui zero i ZF NO s'estableixi (és a dir, sigui zero). Si es compleixen aquestes condicions, salta a l'etiqueta. En cas contrari, cau.

Amb x64, el registre RCX o les seves subparts com ECX o CX, conté el nombre enter del comptador. Amb les instruccions LOOP, el comptador normalment fa un compte enrere, disminuint en 1 per cada salt (bucle). En el següent segment de codi de bucle, el nombre del registre EAX augmenta de 0 a 10 en deu iteracions mentre que el nombre d'ECX compta (disminueix) 10 vegades (llegiu els comentaris):

MOV EAX, 0;

MOV ECX, 10; compte enrere 10 vegades per defecte, una vegada per cada iteració

etiqueta:

INC EAX ; incrementeu EAX com a cos del bucle

etiqueta LOOP; disminuïu EAX i, si EAX no és zero, torneu a executar el cos del bucle des de 'label:'

La codificació del bucle comença des de 'label:'. Tingueu en compte l'ús dels dos punts. La codificació del bucle acaba amb l''etiqueta LOOP' que diu disminueix EAX. Si el seu contingut no és zero, torneu a la instrucció després de 'label:' i torneu a executar qualsevol instrucció (totes les instruccions del cos) que baixi fins a 'LOOP label'. Tingueu en compte que 'etiqueta' encara pot tenir un altre nom.

6.36 Entrada/sortida de x64

Aquesta secció del capítol tracta d'enviar les dades a un port de sortida (intern) o rebre les dades des d'un port d'entrada (intern). El chipset té ports de vuit bits. Qualsevol dos ports consecutius de 8 bits es poden tractar com un port de 16 bits i qualsevol quatre ports consecutius poden ser un port de 32 bits. D'aquesta manera, el processador pot transferir 8, 16 o 32 bits a o des d'un dispositiu extern.

La informació es pot transferir entre el processador i un port intern de dues maneres: utilitzant el que es coneix com a entrada/sortida assignada a memòria o utilitzant un espai d'adreces d'entrada/sortida independent. L'E/S assignada a la memòria és com el que passa amb el processador 6502 on les adreces de port formen part de tot l'espai de memòria. En aquest cas, quan s'envien les dades a una ubicació d'adreça concreta, es dirigeixen a un port i no a un banc de memòria. Els ports poden tenir un espai d'adreces d'E/S independent. En aquest darrer cas, tots els bancs de memòria tenen les seves adreces des de zero. Hi ha un rang d'adreces independent de 0000H a FFFF16. Aquests són utilitzats pels ports del chipset. La placa base està programada per no confondre entre E/S assignades a memòria i espai d'adreces d'E/S independent.

E/S assignades amb memòria

Amb això, els ports es consideren ubicacions de memòria i els codis operatius normals que s'utilitzen entre la memòria i µP s'utilitzen per a la transferència de dades entre µP i ports. Per tant, per moure un byte d'un port a l'adreça F000H al registre µP RAX:EAX:AX:AL, feu el següent:

MOV AL, [F000H]

Una cadena es pot moure de la memòria a un port i viceversa. Exemple:

MOVS [F000H], [C000H] ; la font és C000H i la destinació és el port a F000H.

Espai d'adreces d'E/S separat

Amb això, s'han d'utilitzar les instruccions especials d'entrada i sortida.

Transferència d'elements individuals

El registre del processador per a la transferència és RAX. De fet, és RAX:EAX per a paraula doble, RAX:EAX:AX per paraula i RAX:EAX:AX:AL per a byte. Per tant, per transferir un byte d'un port a FFF0h, a RAX:EAX:AX:AL, escriviu el següent:

IN AL, [FFF0H]

Per a la transferència inversa, escriviu el següent:

OUT [FFF0H], AL

Per tant, per a articles individuals, les instruccions són IN i OUT. L'adreça del port també es pot donar al registre RDX:EDX:DX.

Transferència de cadenes

Es pot transferir una cadena des de la memòria a un port de chipset i viceversa. Per transferir una cadena des d'un port a l'adreça FFF0H a la memòria, comenceu a C100H, escriviu:

INS [ESI], [DX]

que té el mateix efecte que:

INS [EDI], [DX]

El programador hauria de posar l'adreça del port de dos bytes de FFF0H al registre RDX:EDX:Dx i l'adreça de dos bytes de C100H al registre RSI:ESI o RDI:EDI. Per a la transferència inversa, feu el següent:

INS [DX], [ESI]

que té el mateix efecte que:

INS [DX], [EDI]

6.37 La pila en x64

Igual que el processador 6502, el processador x64 també té una pila a la memòria RAM. La pila per al x64 pot ser 2 16 = 65.536 bytes de llarg o pot ser 2 32 = 4.294.967.296 bytes de llarg. També creix cap avall. Quan el contingut d'un registre s'envia a la pila, el número del punter de la pila RSP es redueix en 8. Recordeu que una adreça de memòria per a x64 té 64 bits d'amplada. El valor del punter de pila del µP apunta a la següent ubicació de la pila a la memòria RAM. Quan el contingut d'un registre (o un valor d'un operand) surt de la pila a un registre, el nombre del punter de pila RSP augmenta en 8. El sistema operatiu decideix la mida de la pila i on comença a la RAM. i creix cap avall. Recordeu que una pila és una estructura Last-In-First-Out (LIFO) que creix cap avall i es redueix cap amunt en aquest cas.

Per enviar el contingut del registre µP RBX a la pila, feu el següent:

PUSH RBX

Per tornar l'última entrada de la pila a RBX, feu el següent:

POP RBX

6.38 Procediment en x64

La subrutina del x64 s'anomena 'procediment'. La pila s'utilitza aquí més del que s'utilitza per al 6502 µP. La sintaxi d'un procediment x64 és:

nom_proc:

òrgan del procediment

…

dret

Abans de continuar, observeu que els codis operatius i les etiquetes d'una subrutina x64 (instruccions de llenguatge ensamblador en general) no distingeixen entre majúscules i minúscules. És a dir proc_name és el mateix que PROC_NAME. Igual que el 6502, el nom del nom del procediment (etiqueta) comença al començament d'una nova línia a l'editor de text per al llenguatge assemblador. Això és seguit per dos punts i no per l'espai i el codi operatiu com amb el 6502. El cos de la subrutina segueix, acabant amb RET i no RTS com amb el 6502 µP. Igual que amb el 6502, cada instrucció del cos, inclòs RET, no comença al principi de la seva línia. Tingueu en compte que una etiqueta aquí pot tenir més de 8 caràcters. Per cridar aquest procediment, des de dalt o per sota del procediment mecanografiat, feu el següent:

CALL proc_name

Amb el 6502, el nom de l'etiqueta és només el tipus de trucada. Tanmateix, aquí s'escriu la paraula reservada 'CALL' o 'trucada', seguida del nom del procediment (subrutina) després d'un espai.

Quan es tracta de procediments, normalment hi ha dos procediments. Un procediment crida a l'altre. El procediment que truca (té la instrucció de trucada) s'anomena 'callador', i el procediment que s'anomena s'anomena 'called'. Hi ha una convenció (regles) a seguir.

Regles de la persona que truca

La persona que truca ha de complir les regles següents quan invoqui una subrutina:

1. Abans de trucar a una subrutina, la persona que truca hauria de desar el contingut de determinats registres designats com a desats de la persona que truca per apilar-los. Els registres desats per la persona que truca són R10, R11 i qualsevol registre en què s'introdueixen els paràmetres (RDI, RSI, RDX, RCX, R8, R9). Si el contingut d'aquests registres s'ha de preservar a través de la trucada de subrutina, introduïu-los a la pila en lloc de desar-lo a la memòria RAM. S'han de fer perquè els registres han de ser utilitzats pel destinatari per esborrar els continguts anteriors.

2. Si el procediment és sumar dos números per exemple, els dos números són els paràmetres que cal passar a la pila. Per passar els paràmetres a la subrutina, col·loqueu sis d'ells en els registres següents per ordre: RDI, RSI, RDX, RCX, R8, R9. Si hi ha més de sis paràmetres a la subrutina, premeu la resta a la pila en ordre invers (és a dir, primer paràmetre). Com que la pila creix cap avall, el primer dels paràmetres addicionals (en realitat el setè paràmetre) s'emmagatzema a l'adreça més baixa (aquesta inversió de paràmetres s'utilitzava històricament per permetre que les funcions (subrutines) es transmetessin amb un nombre variable de paràmetres).

3. Per trucar a la subrutina (procediment), utilitzeu la instrucció de trucada. Aquesta instrucció col·loca l'adreça de retorn a la part superior dels paràmetres de la pila (posició més baixa) i les branques al codi de subrutina.

4. Un cop torna la subrutina (és a dir, immediatament després de la instrucció de trucada), la persona que truca ha d'eliminar qualsevol paràmetre addicional (més enllà dels sis que s'emmagatzemen als registres) de la pila. Això restaura la pila al seu estat abans de realitzar la trucada.

5. La persona que truca pot esperar trobar el valor de retorn (adreça) de la subrutina al registre RAX.

6. La persona que truca restaura el contingut dels registres desats per la persona que truca (R10, R11 i qualsevol dels registres de pas de paràmetres) traient-los fora de la pila. La persona que truca pot suposar que la subrutina no ha modificat cap altre registre.

A causa de la forma en què s'estructura la convenció de trucada, normalment es dóna el cas que alguns (o la majoria) d'aquests passos no faran cap canvi a la pila. Per exemple, si hi ha sis paràmetres o menys, no s'introdueix res a la pila en aquest pas. De la mateixa manera, els programadors (i compiladors) solen mantenir els resultats que els importen fora dels registres desats per la persona que truca als passos 1 i 6 per evitar l'excés de pressions i pops.

Hi ha altres dues maneres de passar els paràmetres a una subrutina, però aquestes no s'abordaran en aquest curs de carrera en línia. Un d'ells utilitza la pròpia pila en lloc dels registres de propòsit general.

Regles del carrer

La definició de la subrutina anomenada ha de complir les regles següents:

1. Assignar les variables locals (variables que es desenvolupen dins del procediment) utilitzant els registres o fent espai a la pila. Recordeu que la pila creix cap avall. Per tant, per fer espai a la part superior de la pila, el punter de la pila s'hauria de disminuir. La quantitat en què es disminueix el punter de pila depèn del nombre necessari de variables locals. Per exemple, si es requereix un float local i un llarg local (12 bytes en total), el punter de pila s'ha de disminuir en 12 per fer espai per a aquestes variables locals. En un llenguatge d'alt nivell com C, això significa declarar les variables sense assignar (inicialitzar) els valors.

2. A continuació, s'han de desar els valors de qualsevol registre que sigui el destinatari designat guardat (registres d'ús general no desat per la persona que truca) que s'utilitza per la funció. Per desar els registres, premeu-los a la pila. Els registres desats pel destinatari són RBX, RBP i R12 a R15 (RSP també es conserva per la convenció de trucada, però no cal que s'enviï a la pila durant aquest pas).

Després de realitzar aquestes tres accions, es pot procedir a l'operació real de la subrutina. Quan la subrutina està a punt per tornar, les regles de convenció de trucada continuen.

3. Quan s'hagi acabat la subrutina, el valor de retorn de la subrutina s'ha de col·locar a RAX si encara no hi és.

4. La subrutina ha de restaurar els valors antics de qualsevol registre desat pel destinatari (RBX, RBP i R12 a R15) que s'hagin modificat. Els continguts del registre es restauren traient-los de la pila. Tingueu en compte que els registres s'han d'obrir en l'ordre invers en què es van empènyer.

5. A continuació, desassignem les variables locals. La manera més senzilla de fer-ho és afegir a RSP la mateixa quantitat que se li va restar al pas 1.

6. Finalment, tornem a la persona que truca executant una instrucció ret. Aquesta instrucció trobarà i eliminarà l'adreça de retorn adequada de la pila.

Un exemple del cos d'una subrutina de trucada per trucar a una altra subrutina que és 'myFunc' és el següent (llegiu els comentaris):

; Voleu cridar una funció 'myFunc' que en triga tres

; paràmetre enter. El primer paràmetre es troba a RAX.

; El segon paràmetre és la constant 456. Tercer

; el paràmetre es troba a la ubicació de memòria 'variable'

push rdi ; rdi serà un paràmetre, així que deseu-lo

; long retVal = myFunc ( x , 456 , z ) ;

mov rdi , rax ; posar el primer paràmetre a RDI

mov rsi, 456; poseu el segon paràmetre a RSI

mov rdx , [variable] ; posar el tercer paràmetre a RDX

truca a myFunc; crida a la funció

pop rdi ; restaurar el valor RDI desat

; el valor de retorn de myFunc ja està disponible a RAX

Un exemple de funció de trucada (myFunc) és (llegiu els comentaris):

myFunc:

; ∗∗∗ Pròleg estàndard de subrutina ∗∗∗

sub rsp, 8; espai per a una variable local de 64 bits (resultat) utilitzant el codi operatiu 'sub'.

push rbx; desar els registres del cridat

push rbp; ambdós seran utilitzats per myFunc

; ∗∗∗ Subrutina Cos ∗∗∗

mov rax , rdi ; paràmetre 1 a RAX

mov rbp , rsi ; paràmetre 2 a RBP

mov rbx, rdx; paràmetre 3 a rb x

mov [rsp + 1 6], rbx; posar rbx a la variable local

afegir [rsp + 1 6], rbp; afegir rbp a la variable local

mov rax , [ rsp +16 ] ; mov el contingut de la variable local a RAX

; (valor de retorn/resultat final)

; ∗∗∗ Epíleg de subrutina estàndard ∗∗∗

pop rbp; recuperar els registres de desar el destinatari

pop rbx; invers de quan s'empeny

afegir rsp, 8; desassignar variable(s) local(s). 8 significa 8 bytes

ret ; apareix el valor superior de la pila, salta allà

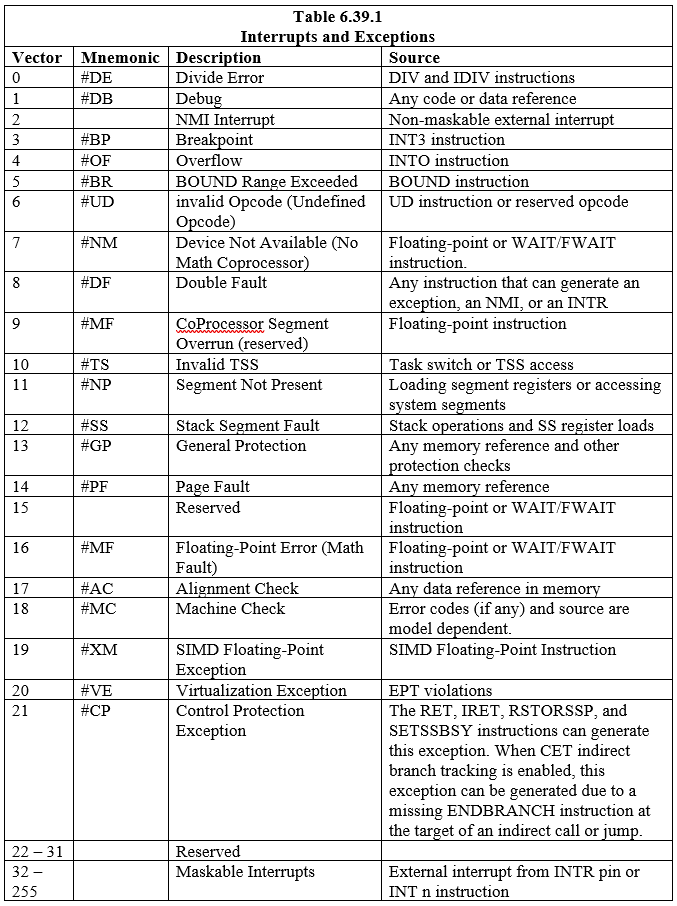

6.39 Interrupcions i excepcions per a x64

El processador proporciona dos mecanismes per interrompre l'execució del programa, interrupcions i excepcions:

- Una interrupció és un esdeveniment asíncron (pot passar en qualsevol moment) que normalment es desencadena per un dispositiu d'E/S.

- Una excepció és un esdeveniment sincrònic (succeeix a mesura que s'executa el codi, preprogramat, en funció d'alguna ocurrència) que es genera quan el processador detecta una o més condicions predefinides mentre executa una instrucció. S'especifiquen tres classes d'excepcions: errors, trampes i avortaments.

El processador respon a les interrupcions i excepcions essencialment de la mateixa manera. Quan s'assenyala una interrupció o una excepció, el processador atura l'execució del programa o tasca actual i canvia a un procediment de controlador escrit específicament per gestionar la condició d'interrupció o excepció. El processador accedeix al procediment del controlador mitjançant una entrada a la taula de descriptors d'interrupcions (IDT). Quan el gestor ha acabat de gestionar la interrupció o l'excepció, el control del programa es retorna al programa o tasca interrompuda.

El sistema operatiu, l'executiu i/o els controladors de dispositiu normalment gestionen les interrupcions i les excepcions independentment dels programes o tasques d'aplicació. Els programes d'aplicació poden, però, accedir als controladors d'interrupcions i excepcions que s'incorporen a un sistema operatiu o executar-lo mitjançant les trucades en llenguatge ensamblador.

Es defineixen divuit (18) interrupcions i excepcions predefinides, que estan associades amb entrades a l'IDT. També es poden fer dues-centes vint-i-quatre (224) interrupcions definides per l'usuari i associar-les a la taula. Cada interrupció i excepció de l'IDT s'identifica amb un número que s'anomena 'vector'. La taula 6.39.1 enumera les interrupcions i excepcions amb entrades a l'IDT i els seus vectors respectius. Els vectors del 0 al 8, del 10 al 14 i del 16 al 19 són les interrupcions i excepcions predefinides. Els vectors del 32 al 255 són per a les interrupcions definides per programari (usuari) que són per a interrupcions de programari o per a interrupcions de maquinari emmascarables.

Quan el processador detecta una interrupció o una excepció, fa una de les accions següents:

- Executeu una crida implícita a un procediment de controlador

- Executeu una crida implícita a una tasca de controlador

6.4 Conceptes bàsics de l'arquitectura d'ordinadors ARM de 64 bits

Les arquitectures ARM defineixen una família de processadors RISC adequats per al seu ús en una gran varietat d'aplicacions. ARM és una arquitectura de càrrega/emmagatzematge que requereix que les dades es carreguin de la memòria a un registre abans que qualsevol processament com ara una operació ALU (Unitat lògica aritmètica) pugui tenir lloc amb ell. Una instrucció posterior emmagatzema el resultat a la memòria. Tot i que això pot semblar un pas enrere respecte a les arquitectures x86 i x64, que operen directament sobre els operands de la memòria en una única instrucció (utilitzant registres de processador, és clar), l'enfocament de càrrega/emmagatzematge, a la pràctica, permet diverses operacions seqüencials. es realitzarà a gran velocitat en un operand un cop carregat en un dels molts registres del processador. Els processadors ARM tenen l'opció de ser petit o gran. La configuració predeterminada d'ARM 64 és little-endian, que és la configuració que utilitzen habitualment els sistemes operatius. L'arquitectura ARM de 64 bits és moderna i està configurada per substituir l'arquitectura ARM de 32 bits.

Nota : Cada instrucció per a l'ARM µP de 64 bits té una longitud de 4 bytes (32 bits).

6.41 El conjunt de registres ARM de 64 bits

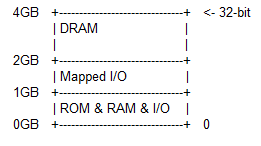

Hi ha 31 registres de propòsit general de 64 bits per a l'ARM µP de 64 bits. El diagrama següent mostra els registres de propòsit general i alguns registres importants:

Fig.4.11.1 Propòsit general de 64 bits i alguns registres importants

Els registres de propòsit general es coneixen com a X0 a X30. La primera part de 32 bits per a cada registre s'anomena W0 a W30. Quan no es posa èmfasi en la diferència entre 32 bits i 64 bits, s'utilitza el prefix 'R'. Per exemple, R14 es refereix a W14 o X14.

El 6502 µP té un comptador de programes de 16 bits i pot adreçar el 2 16 ubicacions de bytes de memòria. L'ARM µP de 64 bits té un comptador de programes de 64 bits i pot adreçar fins a 2 64 = 1,844674407 x 1019 (en realitat 18.446.744.073.709.551.616) ubicacions de bytes de memòria. El comptador del programa conté l'adreça de la següent instrucció a executar. La longitud de la instrucció de l'ARM64 o AArch64 sol ser de quatre bytes. El processador augmenta automàticament aquest registre en quatre després que cada instrucció s'obtingui de la memòria.

El registre Stack Pointer o SP no es troba entre els 31 registres de propòsit general. El punter de pila de qualsevol arquitectura apunta a l'última entrada de pila de la memòria. Per a l'ARM-64, la pila creix cap avall.

El 6502 µP té un registre d'estat del processador de 8 bits. L'equivalent a l'ARM64 s'anomena registre PSTATE. Aquest registre emmagatzema els indicadors que s'utilitzen per als resultats de les operacions i per controlar el processador (µP). Té una amplada de 32 bits. La taula següent ofereix els noms, l'índex i els significats dels bits utilitzats habitualment al registre PSTATE:

| Taula 6.41.1 Senyals PSTATE més utilitzats (bits) |

||

|---|---|---|

| Símbol | Bit | Propòsit |

| M | 0-3 | Mode: el nivell de privilegi d'execució actual (USR, SVC, etc.). |

| T | 4 | Polze: s'estableix si el conjunt d'instruccions T32 (polze) està actiu. Si està clar, el conjunt d'instruccions ARM està actiu. El codi d'usuari pot configurar i esborrar aquest bit. |

| I | 9 | Endianness: establir aquest bit habilita el mode big-endian. Si està clar, el mode little-endian està actiu. El mode predeterminat és el mode little-endian. |

| Q | 27 | Bandera de saturació acumulada: s'estableix si, en algun moment d'una sèrie d'operacions, es produeix un desbordament o saturació. |

| EN | 28 | Marcador de desbordament: s'estableix si l'operació ha donat lloc a un desbordament signat. |

| C | 29 | Bandera de transport: indica si la suma ha produït un acarreament o la resta ha produït un préstec. |

| AMB | 30 | Marca zero: s'estableix si el resultat d'una operació és zero. |

| N | 31 | Marcador negatiu: S'estableix si el resultat d'una operació és negatiu. |

L'ARM-64 µP té molts altres registres.

SIMD

SIMD són les sigles de Single Instruction, Multiple Data. Això vol dir que una instrucció de llenguatge ensamblador pot actuar sobre diverses dades al mateix temps en un microprocessador. Hi ha trenta-dos registres de 128 bits d'ample per utilitzar-los amb SIMD i operacions de coma flotant.

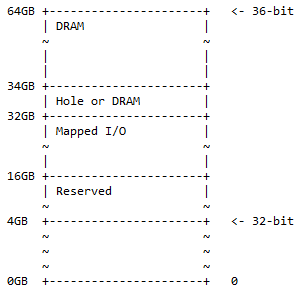

6.42 Mapes de memòria

La memòria RAM i la DRAM són memòries d'accés aleatori. La DRAM funciona més lenta que la RAM. La DRAM és més barata que la RAM. Si hi ha més de 32 gigabytes (GB) de DRAM continua a la memòria, hi haurà més problemes de gestió de memòria: 32 GB = 32 x 1024 x 1024 x 1024 bytes. Per a tot un espai de memòria que sigui molt més gran que 32 GB, la DRAM per sobre de 32 GB s'hauria d'intercalar amb RAM per a una millor gestió de la memòria. Per entendre el mapa de memòria ARM-64, primer hauríeu d'entendre el mapa de memòria de 4 GB per a la unitat de processament central (CPU) ARM de 32 bits. CPU significa µP. Per a un ordinador de 32 bits, l'espai màxim de memòria adreçable és 2 32 = 4 x 2 10 x 2 10 x 2 10 = 4 x 1024 x 1024 x 1024 = 4.294.967.296 = 4 GB.

Mapa de memòria ARM de 32 bits

El mapa de memòria per a un ARM de 32 bits és:

Per a un ordinador de 32 bits, la mida màxima de tota la memòria és de 4 GB. Des de l'adreça de 0 GB fins a l'adreça d'1 GB hi ha el sistema operatiu ROM, la memòria RAM i les ubicacions d'E/S. Tota la idea del sistema operatiu ROM, la memòria RAM i les adreces d'E/S és similar a la situació del Commodore-64 amb una possible CPU 6502. La ROM del sistema operatiu per al Commodore-64 es troba a l'extrem superior de l'espai de memòria. El sistema operatiu ROM aquí és molt més gran que el del Commodore-64 i es troba al principi de tot l'espai d'adreces de memòria. En comparació amb altres ordinadors moderns, el sistema operatiu ROM aquí és complet, en el sentit que és comparable amb la quantitat de sistema operatiu dels seus discs durs. Hi ha dues raons principals per tenir el sistema operatiu als circuits integrats ROM: 1) Les CPU ARM s'utilitzen principalment en dispositius petits com els telèfons intel·ligents. Molts discs durs són més grans que els telèfons intel·ligents i altres dispositius petits, 2) per seguretat. Quan el sistema operatiu es troba a la memòria de només lectura, els pirates informàtics no poden danyar-se (les parts sobreescriuen). Les seccions de RAM i les seccions d'entrada/sortida també són molt grans en comparació amb les del Commodore-64.

Quan s'engega l'alimentació amb el sistema operatiu ROM de 32 bits, el sistema operatiu ha d'iniciar-se des de l'adreça 0x00000000 o l'adreça 0xFFFF0000 si HiVECs està habilitat. Així, quan s'engega l'alimentació després de la fase de restabliment, el maquinari de la CPU carrega 0x00000000 o 0xFFFF0000 al comptador de programes. El prefix '0x' significa hexadecimal. L'adreça d'arrencada de les CPU ARMv8 de 64 bits és una implementació definida. No obstant això, l'autor aconsella a l'enginyer informàtic que comenci a 0x00000000 o 0xFFFF0000 per garantir la compatibilitat enrere.

D'1 GB a 2 GB és l'entrada/sortida assignada. Hi ha una diferència entre les E/S assignades i només les E/S que es troben entre 0 GB i 1 GB. Amb E/S, l'adreça de cada port es fixa com amb el Commodore-64. Amb l'E/S mapejada, l'adreça de cada port no és necessàriament la mateixa per a cada operació de l'ordinador (dinàmica).

De 2 GB a 4 GB és DRAM. Aquesta és la memòria RAM esperada (o habitual). DRAM significa RAM dinàmica, no és el sentit d'una adreça canviant durant el funcionament de l'ordinador, sinó en el sentit que el valor de cada cel·la de la memòria RAM física s'ha d'actualitzar a cada pols de rellotge.

Nota :

- De 0x0000,0000 a 0x0000, FFFF és la ROM del sistema operatiu.

- Des de 0x0001,0000 fins a 0x3FFF, FFFF, hi pot haver més ROM, després RAM i després alguna E/S.

- De 0x4000,0000 a 0x7FFF,FFFF, es permet una E/S addicional i/o una E/S assignada.

- De 0x8000,0000 a 0xFFFF, FFFF és la DRAM esperada.

Això vol dir que la DRAM esperada no ha de començar al límit de la memòria de 2 GB, a la pràctica. Per què el programador hauria de respectar els límits ideals quan no hi ha prou bancs de RAM físics que estiguin connectats a la placa base? Això es deu al fet que el client no té prou diners per a tots els bancs de RAM.

Mapa de memòria ARM de 36 bits

Per a un ordinador ARM de 64 bits, tots els 32 bits s'utilitzen per adreçar tota la memòria. Per a un ordinador ARM de 64 bits, els primers 36 bits es poden utilitzar per adreçar tota la memòria que, en aquest cas, és 2 36 = 68.719.476.736 = 64 GB. Això ja és molt de memòria. Els ordinadors corrents d'avui no necessiten aquesta quantitat de memòria. Això encara no arriba al rang màxim de memòria a què es pot accedir amb 64 bits. El mapa de memòria per a 36 bits per a la CPU ARM és:

De l'adreça de 0 GB a l'adreça de 4 GB hi ha el mapa de memòria de 32 bits. 'Reservat' vol dir que no s'utilitza i es conserva per a un ús futur. No han de ser bancs de memòria física que estiguin connectats a la placa base per a aquest espai. Aquí, la DRAM i les E/S assignades tenen els mateixos significats que per al mapa de memòria de 32 bits.

A la pràctica es pot trobar la situació següent:

- 0x1 0000 0000 – 0x3 FFFF FFFF; reservat. Es reserven 12 GB d'espai d'adreces per a un ús futur.

- 0x4 0000 0000 – 0x7 FFFF FFFF; E/S mapejades. Hi ha 16 GB d'espai d'adreces disponible per a E/S mapejades dinàmicament.

- 0x8 0000 0000 – 0x8 7FFF FFFF FFFF; Forat o DRAM. 2 GB d'espai d'adreces poden contenir qualsevol dels elements següents:

- Forat per habilitar la partició del dispositiu DRAM (tal com es descriu a la discussió següent).

- DRAM.

- 0x8 8000 0000 – 0xF FFFF FFFF; DRAM. 30 GB d'espai d'adreces per a DRAM.

Aquest mapa de memòria és un superconjunt del mapa d'adreces de 32 bits, amb l'espai addicional dividit en un 50% de DRAM (1/2) amb un forat opcional i un 25% d'espai d'E/S mapat i espai reservat (1/4). ). El 25% restant (1/4) és per al mapa de memòria de 32 bits ½ + ¼ + ¼ = 1.

Nota : De 32 bits a 360 bits és una addició de 4 bits al costat més significatiu de 36 bits.

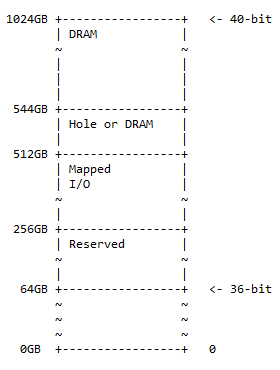

Mapa de memòria de 40 bits

El mapa d'adreces de 40 bits és un superconjunt del mapa d'adreces de 36 bits i segueix el mateix patró de 50% de DRAM d'un forat opcional, un 25% d'espai d'E/S mapejat i espai reservat, i la resta del 25% espai per al mapa de memòria anterior (36 bits). El diagrama per al mapa de memòria és:

La mida del forat és de 544 – 512 = 32 GB. A la pràctica es pot trobar la situació següent:

- 0x10 0000 0000 – 0x3F FFFF FFFF; reservat. 192 GB d'espai d'adreces estan reservats per a un ús futur.

- 0x40 0000 0000 – 0x7F FFFF FFFF; cartografiat. E/S Hi ha disponible 256 GB d'espai d'adreces per a E/S assignades dinàmicament.

- 0x80 0000 0000 – 0x87 FFFF FFFF; forat o DRAM. 32 GB d'espai d'adreces poden contenir qualsevol dels elements següents:

- Forat per habilitar la partició del dispositiu DRAM (tal com es descriu a la discussió següent)

- DRAM

- 0x88 0000 0000 – 0xFF FFFF FFFF; DRAM. 480 GB d'espai d'adreces per a DRAM.

Nota : De 36 bits a 40 bits és una addició de 4 bits al costat més significatiu de 36 bits.

Forat de DRAM

Al mapa de memòria més enllà dels 32 bits, és un forat de DRAM o una continuació de la DRAM des de la part superior. Quan es tracta d'un forat, cal apreciar el següent: el forat de DRAM proporciona una manera de dividir un dispositiu DRAM gran en diversos rangs d'adreces. El forat DRAM opcional es proposa a l'inici del límit superior de l'adreça DRAM. Això permet un esquema de descodificació simplificat quan es particiona un dispositiu DRAM de gran capacitat a la regió adreçada físicament inferior.

Per exemple, una part de DRAM de 64 GB es subdivideix en tres regions amb els desplaçaments d'adreces realitzats mitjançant una simple resta en els bits d'adreces d'ordre alt de la següent manera:

| Taula 6.42.1 Exemple de partició de DRAM de 64 GB amb forats |

|||

|---|---|---|---|

| Adreces físiques en SoC | Offset | Adreça de DRAM interna | |

| 2 GBytes (mapa de 32 bits) | 0x00 8000 0000 – 0x00 FFFF FFFF | -0x00 8000 0000 | 0x00 0000 0000 – 0x00 7FFF FFFF |

| 30 GBytes (mapa de 36 bits) | 0x08 8000 0000 – 0x0F FFFF FFFF | -0x08 0000 0000 | 0x00 8000 0000 – 0x07 FFFF FFFF |

| 32 GBytes (mapa de 40 bits) | 0x88 0000 0000 – 0x8F FFFF FFFF | -0x80 0000 0000 | 0x08 0000 0000 – 0x0F FFFF FFFF |

Mapes de memòria adreçats de 44 i 48 bits proposats per a CPU ARM

Suposem que un ordinador personal té 1024 GB (= 1 TB) de memòria; això és massa memòria. Per tant, els mapes de memòria adreçada de 44 bits i 48 bits per a les CPU ARM per a 16 TB i 256 TB, respectivament, són només propostes per a les futures necessitats de l'ordinador. De fet, aquestes propostes per a les CPU ARM segueixen la mateixa divisió de memòria per proporció que els mapes de memòria anteriors. És a dir: un 50% de DRAM amb un forat opcional, un 25% d'espai d'E/S i espai reservat, i la resta del 25% d'espai per al mapa de memòria anterior.

Els mapes de memòria adreçada de 52 bits, 56 bits, 60 bits i 64 bits encara s'han de proposar per a l'ARM 64 bits per al futur llunyà. Si els científics en aquell moment encara troben útil la partició 50:25:25 de tot l'espai de memòria, mantindran la proporció.

Nota : SoC significa System-on-Chip que fa referència als circuits del xip µP que d'altra manera no haurien estat allà.

La SRAM o la memòria d'accés aleatori estàtica és més ràpida que la DRAM més tradicional, però requereix més àrea de silici. SRAM no requereix actualització. El lector pot imaginar la memòria RAM com a SRAM.

6.43 Modes d'adreçament en llenguatge ensamblador per a ARM 64

ARM és una arquitectura de càrrega/emmagatzematge que requereix que les dades es carreguin de la memòria a un registre del processador abans que qualsevol processament, com ara una operació lògica aritmètica, pugui tenir lloc amb ell. Una instrucció posterior emmagatzema el resultat a la memòria. Tot i que això pot semblar un pas enrere respecte al x86 i les seves arquitectures x64 posteriors, que operen directament sobre els operands de la memòria en una sola instrucció, a la pràctica, l'enfocament de càrrega/emmagatzematge permet realitzar diverses operacions seqüencials a gran velocitat en un operand un cop carregat en un dels molts registres del processador.

El format del llenguatge assemblador ARM té semblances i diferències amb la sèrie x64 (x86).

- Offset : Es pot afegir una constant signada al registre base. El desplaçament s'escriu com a part de la instrucció. Per exemple: ldr x0, [rx, #10] carrega r0 amb la paraula a l'adreça r1+10.

- Registra't : un increment sense signar que s'emmagatzema en un registre es pot afegir o restar al valor d'un registre base. Per exemple: ldr r0, [x1, x2] carrega r0 amb la paraula a l'adreça x1+x2. Qualsevol dels registres es pot considerar com el registre base.

- Registre a escala : un increment d'un registre es desplaça cap a l'esquerra o cap a la dreta en un nombre especificat de posicions de bit abans de ser afegit o restat del valor del registre base. Per exemple: ldr x0, [x1, x2, lsl #3] carrega r0 amb la paraula a l'adreça r1+(r2×8). El desplaçament pot ser un desplaçament lògic a l'esquerra o a la dreta (lsl o lsr) que insereix bits zero a les posicions de bits desocupats o un desplaçament aritmètic a la dreta (asr) que replica el bit de signe a les posicions desocupades.

Quan hi ha dos operands implicats, la destinació arriba abans (a l'esquerra) de la font (hi ha algunes excepcions). Els codis operatius per al llenguatge ensamblador ARM no distingeixen entre majúscules i minúscules.

Mode d'adreçament ARM64 immediat

Exemple:

mov r0, #0xFF000000 ; Carregueu el valor de 32 bits FF000000h a r0

Un valor decimal no té 0x però encara va precedit de #.

Registre directe

Exemple:

mov x0, x1 ; Copia x1 a x0

Registre indirecte

Exemple:

str x0, [x3] ; Emmagatzema x0 a l'adreça de x3

Registre indirecte amb Offset

Exemples:

ldr x0, [x1, #32] ; Carregueu r0 amb el valor a l'adreça [r1+32]; r1 és el registre base

str x0, [x1, #4] ; Emmagatzema r0 a l'adreça [r1+4]; r1 és el registre base; els números són de base 10

Registre indirecte amb compensació (preincrementat)

Exemples:

ldr x0, [x1, #32]! ; Carregueu r0 amb [r1+32] i actualitzeu r1 a (r1+32)

str x0, [x1, #4]! ; Emmagatzema r0 a [r1+4] i actualitza r1 a (r1+4)

Tingueu en compte l'ús del '!' símbol.

Registre indirecte amb compensació (post-increment)

Exemples:

ldr x0, [x1], #32 ; Carregueu [x1] a x0 i, a continuació, actualitzeu x1 a (x1+32)

str x0, [x1], #4 ; Emmagatzema x0 a [x1] i, a continuació, actualitza x1 a (x1+4)

Doble registre indirecte

L'adreça de l'operand és la suma d'un registre base i un registre d'increment. Els noms del registre estan envoltats per claudàtors.

Exemples:

ldr x0, [x1, x2] ; Carrega x0 amb [x1+x2]

str x0, [rx, x2] ; Emmagatzema x0 a [x1+x2]

Mode d'adreçament relatiu

En el mode d'adreçament relatiu, la instrucció efectiva és la següent instrucció del comptador de programes, més un índex. L'índex pot ser positiu o negatiu.

Exemple:

ldr x0, [peça, #24]

Això significa el registre de càrrega X0 amb la paraula a la qual apunta el contingut de l'ordinador més 24.

6.44 Algunes instruccions d'ús habitual per a ARM 64

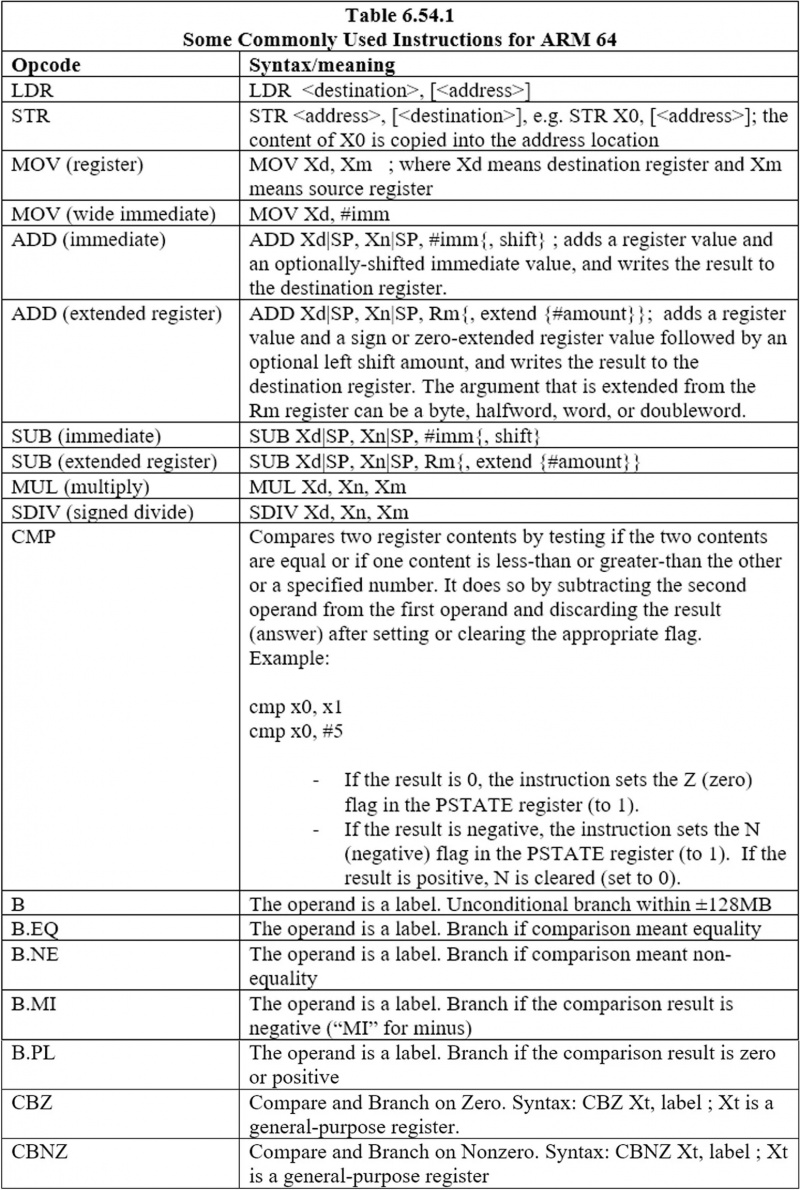

Aquestes són les instruccions d'ús habitual:

6.45 Bucle

Il·lustració

El codi següent continua afegint el valor del registre X10 al valor de X9 fins que el valor de X8 sigui zero. Suposem que tots els valors són nombres enters. El valor de X8 es resta 1 en cada iteració:

bucle:

CBZ X8, salteu

AFEGIR X9, X9, X10 ; el primer X9 és la destinació i el segon X9 és l'origen

SUB X8, X8, #1 ; el primer X8 és la destinació i el segon X8 és l'origen

Bucle B

Omet:

Igual que amb el 6502 µP i el X64 µP, l'etiqueta de l'ARM 64 µP comença al principi de la línia. La resta de les instruccions comencen en alguns espais després de l'inici de la línia. Amb x64 i ARM 64, l'etiqueta va seguida de dos punts i una línia nova. Mentre que amb 6502, l'etiqueta va seguida d'una instrucció després d'un espai. Al codi anterior, la primera instrucció que és 'CBZ X8, saltar' vol dir que si el valor de X8 és zero, continueu a l'etiqueta 'ometeu:', ometeu-vos les instruccions intermedis i continueu amb la resta de les instruccions següents. 'Omet:'. 'Bucle B' és un salt incondicional a l'etiqueta 'bucle'. Es pot utilitzar qualsevol altre nom d'etiqueta en lloc de 'bucle'.

Així, com amb el 6502 µP, utilitzeu les instruccions de la branca per tenir un bucle amb l'ARM 64.

6.46 ARM 64 Entrada/sortida

Tots els perifèrics ARM (ports interns) estan assignats a memòria. Això vol dir que la interfície de programació és un conjunt de registres adreçats a memòria (ports interns). L'adreça d'aquest registre és un desplaçament d'una adreça de base de memòria específica. Això és similar a com el 6502 fa l'entrada/sortida. ARM no té l'opció d'espai d'adreces d'E/S independent.

6.47 Pila de ARM 64

L'ARM 64 té una pila de memòria (RAM) d'una manera similar a la que tenen els 6502 i x64. Tanmateix, amb l'ARM64, no hi ha cap codi d'operació push o pop. La pila a ARM 64 també creix cap avall. L'adreça del punter de pila apunta just després de l'últim byte de l'últim valor que es col·loca a la pila.

La raó per la qual no hi ha cap codi d'operació pop o push genèric per a l'ARM64 és que ARM 64 gestiona la seva pila en grups de 16 bytes consecutius. Tanmateix, els valors existeixen en grups de bytes d'un byte, dos bytes, quatre bytes i 8 bytes. Per tant, un valor es pot col·locar a la pila i la resta de llocs (ubicacions de bytes) per compensar 16 bytes s'omplen amb bytes ficticis. Això té l'inconvenient de perdre la memòria. Una millor solució és omplir la ubicació de 16 bytes amb valors més petits i tenir algun codi escrit per programador que faci un seguiment d'on provenen els valors de la ubicació de 16 bytes (registres). Aquest codi addicional també és necessari per retirar els valors. Una alternativa a això és omplir dos registres de propòsit general de 8 bytes amb els diferents valors i després enviar el contingut dels dos registres de 8 bytes a una pila. Encara es necessita un codi addicional aquí per fer un seguiment dels petits valors específics que entren a la pila i surten de la pila.

El codi següent emmagatzema quatre dades de 4 bytes a la pila:

str w0, [sp, #-4]!

str w1, [sp, #-8]!

str w2, [sp, #-12]!

str w3, [sp, #-16]!

Els primers quatre bytes (w) de registres (x0, x1, x2 i x3) s'envien a ubicacions de 16 bytes consecutius a la pila. Tingueu en compte l'ús de 'str' i no de 'empènyer'. Observeu el símbol d'exclamació al final de cada instrucció. Com que la pila de memòria creix cap avall, el primer valor de quatre bytes comença en una posició que està menys quatre bytes per sota de la posició anterior del punter de pila. La resta de valors de quatre bytes segueixen, baixant. El següent segment de codi farà l'equivalent correcte (i en ordre) d'explotar els quatre bytes:

ldr w3, [sp], #0

ldr w2, [sp], #4

ldr w1, [sp], #8

ldr w0, [sp], #12

Tingueu en compte l'ús del codi operatiu ldr en comptes de pop. Tingueu en compte també que el símbol d'exclamació no s'utilitza aquí.

Tots els bytes de X0 (8 bytes) i X1 (8 bytes) es poden enviar a la ubicació de 16 bytes de la pila de la manera següent:

stp x0, x1, [sp, #-16]! ; 8 + 8 = 16

En aquest cas, els registres x2 (w2) i x3 (w3) no són necessaris. Tots els bytes desitjats es troben als registres X0 i X2. Tingueu en compte el codi operatiu stp per emmagatzemar els parells de continguts del registre a la memòria RAM. Tingueu en compte també el símbol d'exclamació. L'equivalent pop és:

ldp x0, x1, [sp], #0

No hi ha cap signe d'exclamació per a aquesta instrucció. Tingueu en compte el codi operatiu LDP en lloc de LDR per carregar dues ubicacions de dades consecutives de la memòria a dos registres µP. Recordeu també que la còpia de la memòria a un registre µP s'està carregant, que no s'ha de confondre amb la càrrega d'un fitxer del disc a la memòria RAM, i la còpia d'un registre µP a la memòria RAM s'emmagatzema.

6.48 Subrutina

Una subrutina és un bloc de codi que realitza una tasca, opcionalment basada en alguns arguments i opcionalment retorna un resultat. Per convenció, els registres R0 a R3 (quatre registres) s'utilitzen per passar els arguments (paràmetres) a una subrutina, i R0 s'utilitza per tornar un resultat a la persona que truca. Una subrutina que necessita més de 4 entrades utilitza la pila per a les entrades addicionals. Per trucar a una subrutina, utilitzeu l'enllaç o la instrucció de branca condicional. La sintaxi de la instrucció d'enllaç és:

Etiqueta BL

On BL és el codi operatiu i l'etiqueta representa l'inici (adreça) de la subrutina. Aquesta branca és incondicional, endavant o enrere en 128 MB. La sintaxi de la instrucció de branca condicional és:

B.cond etiqueta

On cond és la condició, per exemple, eq (igual) o ne (no igual). El programa següent té la subrutina doadd que afegeix els valors de dos arguments i retorna un resultat a R0:

AREA subroute, CODE, READONLY ; Anomena aquest bloc de codi

ENTRADA ; Marqueu la primera instrucció a executar

iniciar MOV r0, #10; Configura els paràmetres

MOV r1, #3

BL doadd ; Subrutina de trucada

aturar MOV r0, #0x18 ; angel_SWIreason_ReportException

LDR r1, =0x20026 ; ADP_Stopped_ApplicationExit

SVC #0x123456 ; Semihosting ARM (anteriorment SWI)

doadd ADD r0, r0, r1; Codi de subrutina

BX lr ; Retorn de la subrutina

;

FINAL ; Marca el final del fitxer

Els nombres a sumar són el decimal 10 i el decimal 3. Les dues primeres línies d'aquest bloc de codi (programa) s'explicaran més endavant. Les tres línies següents envien 10 al registre R0 i 3 al registre R1, i també criden a la subrutina doadd. El 'doadd' és l'etiqueta que conté l'adreça del començament de la subrutina.

La subrutina consta només de dues línies. La primera línia afegeix el contingut 3 de R al contingut 10 de R0 que permet el resultat de 13 a R0. La segona línia amb el codi operatiu BX i l'operand LR torna de la subrutina al codi de trucada.

DRET

El codi operatiu RET a ARM 64 encara tracta amb la subrutina, però funciona de manera diferent a RTS a 6502 o RET a x64, o la combinació 'BX LR' a ARM 64. A ARM 64, la sintaxi per a RET és:

RECTE {Xn}

Aquesta instrucció dóna l'oportunitat al programa de continuar amb una subrutina que no és la subrutina de la trucada, o simplement continuar amb una altra instrucció i el seu segment de codi següent. Xn és un registre de propòsit general que conté l'adreça a la qual ha de continuar el programa. Aquesta instrucció es ramifica incondicionalment. Per defecte, el contingut de X30 si no es dóna Xn.

Convocatòria de procediment estàndard

Si el programador vol que el seu codi interaccioni amb un codi escrit per una altra persona o amb un codi produït per un compilador, el programador ha d'acordar amb la persona o l'escriptor del compilador les regles d'ús del registre. Per a l'arquitectura ARM, aquestes regles s'anomenen Procedure Call Standard o PCS. Són acords entre les dues o tres parts. El PCS especifica el següent:

- Quins registres µP s'utilitzen per passar els arguments a la funció (subrutina)

- Quins registres µP s'utilitzen per retornar el resultat a la funció que fa la trucada que es coneix com a persona que truca

- Quin µP registra la funció que s'està cridant, que es coneix com a cridat, pot corrompre's

- Quin µP registra el destinatari no pot corrompre's

6.49 Interrupcions

Hi ha dos tipus de circuits de controlador d'interrupció disponibles per al processador ARM:

- Controlador d'interrupcions estàndard: el controlador d'interrupcions determina quin dispositiu necessita servei llegint un registre de mapa de bits del dispositiu al controlador d'interrupcions.

- Controlador d'interrupcions vectorials (VIC): prioritza les interrupcions i simplifica la determinació de quin dispositiu ha provocat la interrupció. Després d'associar una prioritat i una adreça de controlador amb cada interrupció, el VIC només afirma un senyal d'interrupció al processador si la prioritat d'una nova interrupció és superior a la del controlador d'interrupció que s'executa actualment.

Nota : L'excepció fa referència a l'error. Els detalls del controlador d'interrupció vectorial per a l'ordinador ARM de 32 bits són els següents (64 bits és similar):

| Taula 6.49.1 Excepció/interrupció del vector ARM per a ordinadors de 32 bits |

|||

|---|---|---|---|

| Excepció/Interrupció | Mà curta | adreça | Adreça alta |

| Restableix | RESET | 0x00000000 | 0xffff0000 |

| Instrucció indefinida | UNDEF | 0x00000004 | 0xffff0004 |

| Interrupció de programari | SWI | 0x00000008 | 0xffff0008 |

| Avorta la recuperació prèvia | pabt | 0x0000000C | 0xffff000C |

| Data de l'avortament | DABT | 0x00000010 | 0xffff0010 |

| Reservat | – | 0x00000014 | 0xffff0014 |

| Sol·licitud d'interrupció | IRQ | 0x00000018 | 0xffff0018 |

| Sol·licitud d'interrupció ràpida | FIQ | 0x0000001C | 0xffff001C |

Sembla la disposició de l'arquitectura 6502 on NMI , BR , i IRQ pot tenir punters a la pàgina zero, i les rutines corresponents estan a la part alta de la memòria (SO ROM). Les descripcions breus de les files de la taula anterior són les següents:

RESET

Això passa quan el processador s'encén. Inicialitza el sistema i configura les piles per a diferents modes de processador. És l'excepció de màxima prioritat. En entrar al controlador de restabliment, el CPSR està en mode SVC i els bits IRQ i FIQ s'estableixen a 1, emmascarant qualsevol interrupció.

DATA DE L'ABORTAMENT

La segona prioritat. Això passa quan intentem llegir/escriure en una adreça no vàlida o accedir a un permís d'accés incorrecte. En entrar al gestor d'avortament de dades, les IRQ es desactivaran (conjunt de bits I 1) i s'habilitarà el FIQ. Les IRQ estan emmascarades, però les FIQ es mantenen desemmascarades.

FIQ

La interrupció de màxima prioritat, IRQ i FIQ, es desactiva fins que es gestiona FIQ.

IRQ

La interrupció d'alta prioritat, el controlador IRQ, només s'introdueix si no hi ha cap FIQ i avortament de dades en curs.

Avorta la recuperació prèvia

Això és semblant a l'avortament de dades, però es produeix quan falla l'obtenció d'adreces. En entrar al controlador, les IRQ es desactiven, però les FIQ romanen habilitades i poden ocórrer durant un avortament previ a la recuperació.

SWI

Es produeix una excepció d'interrupció de programari (SWI) quan s'executa la instrucció SWI i no s'ha marcat cap de les altres excepcions de prioritat més alta.

Instrucció no definida

L'excepció d'instrucció no definida es produeix quan una instrucció que no es troba al conjunt d'instruccions ARM o Thumb arriba a l'etapa d'execució de la canalització i no s'ha marcat cap de les altres excepcions. Aquesta és la mateixa prioritat que SWI, ja que pot passar a la vegada. Això vol dir que la instrucció que s'està executant no pot ser alhora una instrucció SWI i una instrucció no definida.

ARM Gestió d'excepcions

Els esdeveniments següents es produeixen quan es produeix una excepció:

- Emmagatzemeu el CPSR al SPSR del mode d'excepció.

- El PC s'emmagatzema a la LR del mode d'excepció.

- El registre d'enllaç s'estableix a una adreça específica segons la instrucció actual. Per exemple: per a ISR, LR = darrera instrucció executada + 8.

- Actualitzeu el CPSR sobre l'excepció.

- Establiu l'ordinador a l'adreça del controlador d'excepcions.

6.5 Instruccions i dades

Les dades es refereixen a variables (etiquetes amb els seus valors) i matrius i altres estructures que són similars a la matriu. La cadena és com una matriu de caràcters. En un dels capítols anteriors es veu una matriu d'enters. Les instruccions fan referència als codis operatius i als seus operands. Es pot escriure un programa amb els codis operatius i les dades barrejats en una secció continuada de memòria. Aquest enfocament té desavantatges però no es recomana.

Primer s'ha d'escriure un programa amb les instruccions, seguides de les dades (el plural de datum és data). La separació entre les instruccions i les dades només pot ser d'uns quants bytes. Per a un programa, tant les instruccions com les dades poden estar en una o dues seccions separades a la memòria.

6.6 L'arquitectura de Harvard

Un dels primers ordinadors es diu Harvard Mark I (1944). Una arquitectura estricta de Harvard utilitza un espai d'adreces per a les instruccions del programa i un espai d'adreces diferent per a les dades. Això vol dir que hi ha dos records separats. A continuació es mostra l'arquitectura:

Figura 6.71 Arquitectura de Harvard

La Unitat de Control fa la descodificació de les instruccions. La Unitat Aritmètica Lògica (ALU) fa les operacions aritmètiques amb lògica combinacional (portes). ALU també fa les operacions lògiques (per exemple, el canvi).

Amb el microprocessador 6502, una instrucció va primer al microprocessador (unitat de control) abans que la dada (singular per a dades) vagi al registre µP abans que interaccionin. Això necessita almenys dos polsos de rellotge i no és un accés simultani a la instrucció i la dada. D'altra banda, l'arquitectura de Harvard proporciona accés simultani a les instruccions i dades, amb instruccions i dades entrant al µP al mateix temps (codi operatiu a la unitat de control i dada al registre µP), estalviant almenys un pols de rellotge. Aquesta és una forma de paral·lelisme. Aquesta forma de paral·lelisme s'utilitza a la memòria cau de maquinari de les plaques base modernes (consulteu la discussió següent).

6.7 Memòria cau

La memòria cau (RAM) és una regió de memòria d'alta velocitat (en comparació amb la velocitat de la memòria principal) que emmagatzema temporalment les instruccions o dades del programa per a un ús futur. La memòria cau funciona més ràpid que la memòria principal. Normalment, aquestes instruccions o elements de dades es recuperen de la memòria principal recent i és probable que es tornin a necessitar en breu. L'objectiu principal de la memòria cau és augmentar la velocitat d'accés repetit a les mateixes ubicacions de memòria principal. Perquè sigui efectiu, l'accés als elements de la memòria cau ha de ser significativament més ràpid que l'accés a la font original de les instruccions o dades que es coneix com la botiga de suport.

Quan la memòria cau està en ús, cada intent d'accedir a una ubicació de memòria principal comença amb una cerca a la memòria cau. Si l'element sol·licitat està present, el processador el recupera i l'utilitza immediatament. Això s'anomena un èxit de memòria cau. Si la cerca a la memòria cau no té èxit (un error de memòria cau), la instrucció o l'element de dades s'ha de recuperar del magatzem de suport (memòria principal). En el procés de recuperar l'element sol·licitat, s'afegeix una còpia a la memòria cau per a un ús proper previst.

Unitat de gestió de la memòria

La unitat de gestió de memòria (MMU) és un circuit que gestiona la memòria principal i els registres de memòria relacionats a la placa base. En el passat, era un circuit integrat separat a la placa base; però avui en dia, normalment forma part del microprocessador. La MMU també hauria de gestionar la memòria cau (circuit) que també forma part del microprocessador actual. El circuit de memòria cau és un circuit integrat separat en el passat.

RAM estàtica

La RAM estàtica (SRAM) té un temps d'accés substancialment més ràpid que la DRAM, tot i que a costa de circuits significativament més complexos. Les cèl·lules de bits SRAM ocupen molt més espai a la matriu del circuit integrat que les cel·les d'un dispositiu DRAM que és capaç d'emmagatzemar una quantitat equivalent de dades. La memòria principal (RAM) consisteix normalment en DRAM (RAM dinàmica).

La memòria cau millora el rendiment de l'ordinador perquè molts algorismes que s'executen per sistemes operatius i aplicacions mostren la localitat de referència. La localitat de referència fa referència a la reutilització de dades a les quals s'ha accedit recentment. Això es coneix com a localitat temporal. En una placa base moderna, la memòria cau es troba al mateix circuit integrat que el microprocessador. La memòria principal (DRAM) és llunyana i és accessible a través dels autobusos. La localitat de referència també fa referència a la localitat espacial. La localitat espacial té a veure amb la major velocitat d'accés a les dades a causa de la proximitat física.

Com a regla general, les regions de memòria cau són petites (en nombre d'ubicacions de bytes) en comparació amb la botiga de suport (memòria principal). Els dispositius de memòria cau estan dissenyats per a la màxima velocitat, cosa que generalment significa que són més complexos i costosos per bit que la tecnologia d'emmagatzematge de dades que s'utilitza a la botiga de suport. A causa de la seva mida limitada, els dispositius de memòria cau tendeixen a omplir-se ràpidament. Quan una memòria cau no té una ubicació disponible per emmagatzemar una entrada nova, s'ha de descartar una entrada més antiga. El controlador de la memòria cau utilitza una política de substitució de la memòria cau per seleccionar quina entrada de memòria cau es sobreescriurà per la nova entrada.

L'objectiu de la memòria cau del microprocessador és maximitzar el percentatge de visites a la memòria cau al llarg del temps, proporcionant així la taxa més alta d'execució d'instruccions. Per aconseguir aquest objectiu, la lògica de la memòria cau ha de determinar quines instruccions i dades es col·locaran a la memòria cau i es conservaran per a un ús proper.

La lògica d'emmagatzematge a la memòria cau d'un processador no garanteix que un element de dades de la memòria cau es torni a utilitzar un cop s'ha inserit a la memòria cau.

La lògica de la memòria cau es basa en la probabilitat que, a causa de la localitat temporal (que es repeteix al llarg del temps) i espacial (espai), hi ha moltes possibilitats que s'accedeixi a les dades de la memòria cau en un futur proper. En les implementacions pràctiques dels processadors moderns, les visites a la memòria cau normalment es produeixen entre el 95 i el 97 per cent dels accessos a la memòria. Atès que la latència de la memòria cau és una petita fracció de la latència de la DRAM, una alta taxa d'èxit de la memòria cau condueix a una millora substancial del rendiment en comparació amb un disseny sense memòria cau.

Una mica de paral·lelisme amb la memòria cau

Com s'ha esmentat anteriorment, un bon programa a la memòria té les instruccions separades de les dades. En alguns sistemes de memòria cau, hi ha un circuit de memòria cau a la 'esquerra' del processador i hi ha un altre circuit de memòria cau a la 'dreta' del processador. La memòria cau de l'esquerra gestiona les instruccions d'un programa (o aplicació) i la memòria cau de la dreta gestiona les dades del mateix programa (o de la mateixa aplicació). Això condueix a una millor velocitat.

6.8 Processos i fils

Tant els ordinadors CISC com RISC tenen processos. Hi ha un procés al programari. Un programa que s'està executant (executant) és un procés. El sistema operatiu ve amb els seus propis programes. Mentre l'ordinador està funcionant, també s'estan executant els programes del sistema operatiu que permeten que l'ordinador funcioni. Aquests són processos del sistema operatiu. L'usuari o programador pot escriure els seus propis programes. Quan el programa de l'usuari s'està executant, és un procés. No importa si el programa està escrit en llenguatge assemblador o en llenguatge d'alt nivell com C o C++. Tots els processos (usuari o sistema operatiu) són gestionats per un altre procés anomenat 'programador'.

Un fil és com un subprocés que pertany a un procés. Un procés pot començar i dividir-se en fils i després continua com un sol procés. Un procés sense fils es pot considerar com el fil principal. Els processos i els seus fils són gestionats pel mateix planificador. El planificador en si és un programa quan és resident al disc del sistema operatiu. Quan s'executa a la memòria, el planificador és un procés.

6.9 Multiprocessament

Els fils es gestionen gairebé com a processos. Multiprocessament significa executar més d'un procés alhora. Hi ha ordinadors amb un sol microprocessador. Hi ha ordinadors amb més d'un microprocessador. Amb un únic microprocessador, els processos i/o fils utilitzen el mateix microprocessador d'una manera entrellaçada (o segmentant el temps). Això vol dir que un procés utilitza el processador i s'atura sense acabar. Un altre procés o fil utilitza el processador i s'atura sense acabar. Aleshores, un altre procés o fil utilitza el microprocessador i s'atura sense acabar. Això continua fins que tots els processos i fils que es van posar a la cua pel planificador han tingut una part del processador. Això s'anomena multiprocessament simultània.